October 1987 Revised July 2003

# MM74C905

# 12-Bit Successive Approximation Register

### **General Description**

The MM74C905 CMOS 12-bit successive approximation register contains all the digit control and storage necessary for successive approximation analog-to-digital conversion. Because of the unique capability of CMOS to switch to each supply rail without any offset voltage, it can also be used in digital systems as the control and storage element in repetitive routines.

#### **Features**

■ Wide supply voltage range: 3.0V to 15V

- Guaranteed noise margin: 1.0V

- High noise immunity: 0.45 V<sub>CC</sub> (typ)

- Low power TTL compatibility: Fan out of 2 driving 74L

- Provision for register extension or truncation

- Operates in START/STOP or continuous conversion

- Drive ladder switches directly. For 10 bits or less with 50k/100k R/2R ladder network

# **Ordering Code:**

| Order Number | Package Number | Package Description                                                    |

|--------------|----------------|------------------------------------------------------------------------|

| MM74C905N    | N24A           | 24-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-011, 0.600" Wide |

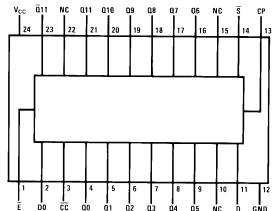

### **Connection Diagram**

#### Pin Assignments for DIP

# **Truth Table**

| Time Inputs    |     |   |   |     |     |     |    | Outp | uts |    |    |    |    |    |    |    |    |

|----------------|-----|---|---|-----|-----|-----|----|------|-----|----|----|----|----|----|----|----|----|

| t <sub>n</sub> | D   | S | E | D0  | Q11 | Q10 | Q9 | Q8   | Q7  | Q6 | Q5 | Q4 | Q3 | Q2 | Q1 | Q0 | CC |

| 0              | Х   | L | L | Х   | Χ   | Х   | Х  | Χ    | Χ   | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Χ  |

| 1              | D11 | Н | L | Х   | L   | Н   | Н  | Н    | Н   | Н  | Н  | Н  | Н  | Н  | Н  | Н  | Н  |

| 2              | D10 | Н | L | D11 | D11 | L   | Н  | Н    | Н   | Н  | Н  | Н  | Н  | Н  | Н  | Н  | Н  |

| 3              | D9  | Н | L | D10 | D11 | D10 | L  | Н    | Н   | Н  | Н  | Н  | Н  | Н  | Н  | Н  | Н  |

| 4              | D8  | Н | L | D9  | D11 | D10 | D9 | L    | Н   | Н  | Н  | Н  | Н  | Н  | Н  | Н  | Н  |

| 5              | D7  | Н | L | D8  | D11 | D10 | D9 | D8   | L   | Н  | Н  | Н  | Н  | Н  | Н  | Н  | Н  |

| 6              | D6  | Н | L | D7  | D11 | D10 | D9 | D8   | D7  | L  | Н  | Н  | Н  | Н  | Н  | Н  | Н  |

| 7              | D5  | Н | L | D6  | D11 | D10 | D9 | D8   | D7  | D6 | L  | Н  | Н  | Н  | Н  | Н  | Н  |

| 8              | D4  | Н | L | D5  | D11 | D10 | D9 | D8   | D7  | D6 | D5 | L  | Н  | Н  | Н  | Н  | Н  |

| 9              | D3  | Н | L | D4  | D11 | D10 | D9 | D8   | D7  | D6 | D5 | D4 | L  | Н  | Н  | Н  | Н  |

| 10             | D2  | Н | L | D3  | D11 | D10 | D9 | D8   | D7  | D6 | D5 | D4 | D3 | L  | Н  | Н  | Н  |

| 11             | D1  | Н | L | D2  | D11 | D10 | D9 | D8   | D7  | D6 | D5 | D4 | D3 | D2 | L  | Н  | Н  |

| 12             | D0  | Н | L | D1  | D11 | D10 | D9 | D8   | D7  | D6 | D5 | D4 | D3 | D2 | D1 | L  | Н  |

| 13             | Χ   | Н | L | D0  | D11 | D10 | D9 | D8   | D7  | D6 | D5 | D4 | D3 | D2 | D1 | D0 | L  |

| 14             | Χ   | Χ | L | Х   | D11 | D10 | D9 | D8   | D7  | D6 | D5 | D4 | D3 | D2 | D1 | D0 | L  |

|                | Χ   | Χ | Н | Х   | Н   | NC  | NC | NC   | NC  | NC | NC | NC | NC | NC | NC | NC | NC |

H = HIGH Level L = LOW Level X = Don't Care NC = No Change

# **Absolute Maximum Ratings**(Note 1)

$\begin{tabular}{lll} \mbox{Voltage at Any Pin} & -0.3\mbox{V to V}_{CC} + 0.3\mbox{V} \\ \mbox{Operating Temperature Range ($T_A$)} & -40\mbox{°C to } +85\mbox{°C} \\ \mbox{Storage Temperature Range ($T_S$)} & -65\mbox{°C to } +150\mbox{°C} \\ \end{tabular}$

Power Dissipation (P<sub>D</sub>)

$\begin{array}{cc} \text{Dual-In-Line} & 700 \text{ mW} \\ \text{Small Outline} & 500 \text{ mW} \\ \text{Operating V}_{\text{CC}} \text{ Range} & 3.0 \text{V to } 15 \text{V} \\ \end{array}$

Absolute Maximum V<sub>CC</sub> 16V

Lead Temperature (T<sub>L</sub>)

(Soldering, 10 seconds) 260°C

**Note 1:** "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. Except for "Operating Temperature Range" they are not meant to imply that the devices should be operated at these limits. The table of "Electrical Characteristics" provides conditions for actual device operation.

#### **DC Electrical Characteristics**

Min/Max limits apply across temperature range unless otherwise noted

| Symbol              | Parameter                         | Conditions                                   | Min                   | Тур    | Max | Units |

|---------------------|-----------------------------------|----------------------------------------------|-----------------------|--------|-----|-------|

| CMOS TO             | CMOS                              |                                              | *                     |        |     |       |

| V <sub>IN(1)</sub>  | Logical "1" Input Voltage         | V <sub>CC</sub> = 5.0V                       | 3.5                   |        |     | V     |

|                     |                                   | V <sub>CC</sub> = 10V                        | 8.0                   |        |     | V     |

| V <sub>IN(0)</sub>  | Logical "0" Input Voltage         | V <sub>CC</sub> = 5.0V                       |                       |        | 1.5 | V     |

|                     |                                   | V <sub>CC</sub> = 10V                        |                       |        | 2.0 | V     |

| V <sub>OUT(1)</sub> | Logical "1" Output Voltage        | $V_{CC} = 5.0V, I_{O} = -10 \mu A$           | 4.5                   |        |     | V     |

|                     |                                   | $V_{CC} = 10V$ , $I_{O} = -10 \mu A$         | 9.0                   |        |     | V     |

| V <sub>OUT(0)</sub> | Logical "0" Output Voltage        | $V_{CC} = 5.0V$ , $I_{O} = 10 \mu A$         |                       |        | 0.5 | V     |

|                     |                                   | $V_{CC} = 10V$ , $I_{O} = 10 \mu A$          |                       |        | 1.0 | V     |

| I <sub>IN(1)</sub>  | Logical "1" Input Current         | V <sub>CC</sub> = 15V, V <sub>IN</sub> = 15V |                       | 0.005  | 1.0 | μΑ    |

| I <sub>IN(0)</sub>  | Logical "0" Input Current         | $V_{CC} = 15V, V_{IN} = 0V$                  | -1.0                  | -0.005 |     | μΑ    |

| I <sub>CC</sub>     | Supply Current                    | V <sub>CC</sub> = 15V                        |                       | 0.05   | 300 | μΑ    |

| CMOS/LP1            | ITL INTERFACE                     |                                              | •                     |        |     |       |

| V <sub>IN(1)</sub>  | Logical "1" Input Voltage         | V <sub>CC</sub> = 4.75V                      | V <sub>CC</sub> - 1.5 |        |     | V     |

| $V_{IN(0)}$         | Logical "0" Input Voltage         | V <sub>CC</sub> = 4.75V                      |                       |        | 0.8 | V     |

| V <sub>OUT(1)</sub> | Logical "1" Output Voltage        | $V_{CC} = 4.75V$ , $I_{O} = -360 \mu A$      | 2.4                   |        |     | V     |

| V <sub>OUT(0)</sub> | Logical "0" Output Voltage        | $V_{CC} = 4.75V$ , $I_{O} = 360 \mu A$       |                       |        | 0.4 | V     |

| OUTPUT D            | ORIVE (See Family Characteristics | Data Sheet)                                  | •                     |        |     |       |

| I <sub>SOURCE</sub> | Output Source Current             | $V_{CC} = 5.0V$ , $V_{OUT} = 0V$             | -1.75                 | -3.3   |     | mA    |

|                     | (P-Channel)                       | T <sub>A</sub> = 25°C                        |                       |        |     |       |

| I <sub>SOURCE</sub> | Output Source Current             | V <sub>CC</sub> = 10V, V <sub>OUT</sub> = 0V | -8.0                  | -15    |     | mA    |

|                     | (P-Channel)                       | $T_A = 25^{\circ}C$                          |                       |        |     |       |

| I <sub>SINK</sub>   | Output Sink Current               | $V_{CC} = 5.0V$ , $V_{OUT} = V_{CC}$         | 1.75                  | 3.6    |     | mA    |

|                     | (N-Channel)                       | T <sub>A</sub> = 25°C                        |                       |        |     |       |

| I <sub>SINK</sub>   | Output Sink Current               | $V_{CC} = 10V$ , $V_{OUT} = V_{CC}$          |                       |        |     |       |

|                     | (N-Channel)                       | T <sub>A</sub> = 25°C                        | 8.0                   | 16     |     | mA    |

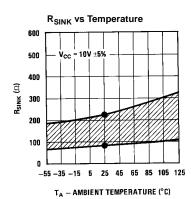

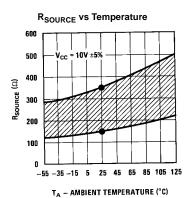

|                     |                                   | $V_{CC} = 10V \pm 5\%$                       |                       |        |     |       |

| R <sub>SOURCE</sub> | Q11–Q0 Outputs                    | $V_{OUT} = V_{CC} - 0.3V$                    | 150                   |        | 350 | Ω     |

|                     |                                   | $T_A = 25^{\circ}C$                          |                       |        |     |       |

| R <sub>SINK</sub>   | Q11–Q0 Outputs                    | V <sub>CC</sub> = 10V ±5%                    |                       |        |     |       |

|                     |                                   | $V_{OUT} = 0.3V$                             | 80                    |        | 230 | Ω     |

|                     |                                   | T <sub>A</sub> = 25°C                        |                       |        |     |       |

# AC Electrical Characteristics (Note 2)

$T_A = 25^{\circ}C$ ,  $C_L = 50$  pF, unless otherwise specified

| Symbol           | Parameter                                | Conditions               | Min | Тур | Max  | Units |

|------------------|------------------------------------------|--------------------------|-----|-----|------|-------|

| t <sub>pd</sub>  | Propagation Delay Time from              | V <sub>CC</sub> = 5.0V   |     | 200 | 350  | ns    |

|                  | Clock Input to Outputs                   | V <sub>CC</sub> = 10V    |     | 80  | 150  | ns    |

|                  | (Q0-Q11) (t <sub>pd(Q)</sub> )           |                          |     |     |      |       |

| pd               | Propagation Delay Time from              | V <sub>CC</sub> = 5.0V   |     | 180 | 325  | ns    |

|                  | Clock Input to D0 (t <sub>pd(D0)</sub> ) | V <sub>CC</sub> = 10V    |     | 70  | 125  | ns    |

| t <sub>pd</sub>  | Propagation Delay Time from              | V <sub>CC</sub> = 5.0V   |     | 190 | 350  | ns    |

|                  | Register Enable (E) to Output            | V <sub>CC</sub> = 10V    |     | 75  | 150  | ns    |

|                  | (Q11) (t <sub>pd(E)</sub> )              |                          |     |     |      |       |

| t <sub>pd</sub>  | Propagation Delay Time from              | V <sub>CC</sub> = 5.0V   |     | 190 | 350  | ns    |

|                  | Clock to CC (t <sub>pd(CC)</sub> )       | V <sub>CC</sub> = 10V    |     | 75  | 0.50 | ns    |

| t <sub>S</sub>   | Data Input Set-Up Time                   | V <sub>CC</sub> = 5.0V   | 80  |     |      | ns    |

|                  |                                          | V <sub>CC</sub> = 10V    | 30  |     |      | ns    |

| t <sub>S</sub>   | Start Input Set-Up Time                  | V <sub>CC</sub> = 5.0V   | 80  |     |      | ns    |

|                  |                                          | V <sub>CC</sub> = 10V    | 30  |     |      | ns    |

| t <sub>W</sub>   | Minimum Clock Pulse Width                | V <sub>CC</sub> = 5.0V   | 250 | 125 |      | ns    |

|                  |                                          | V <sub>CC</sub> = 10V    | 100 | 50  |      | ns    |

| $t_r$ , $t_f$    | Maximum Clock Rise and Fall Time         | V <sub>CC</sub> = 5.0V   |     |     | 15   | μs    |

|                  |                                          | $V_{CC} = 10V$           |     |     | 5.0  | μs    |

| f <sub>MAX</sub> | Maximum Clock Frequency                  | V <sub>CC</sub> = 5.0V   | 2.0 | 4.0 |      | MHz   |

|                  |                                          | V <sub>CC</sub> = 10V    | 5.0 | 10  |      | MHz   |

| C <sub>CK</sub>  | Clock Input Capacitance                  | Clock Input (Note 3)     |     | 10  |      | pF    |

| C <sub>IN</sub>  | Input Capacitance                        | Any other Input (Note 3) |     | 5   |      | pF    |

| C <sub>PD</sub>  | Power Dissipation Capacitance            | (Note 4)                 |     | 100 |      | pF    |

Note 2: AC Parameters are guaranteed by DC correlated testing.

Note 3: Capacitance is guaranteed by periodic testing.

Note 4: C<sub>PD</sub> determines the no load AC power consumption of any CMOS device. For complete explanation, see Family Characteristics Application Note—AN-90.

# **Typical Performance Characteristics**

•These points are guaranteed by automatic testing.

•These points are guaranteed by automatic testing.

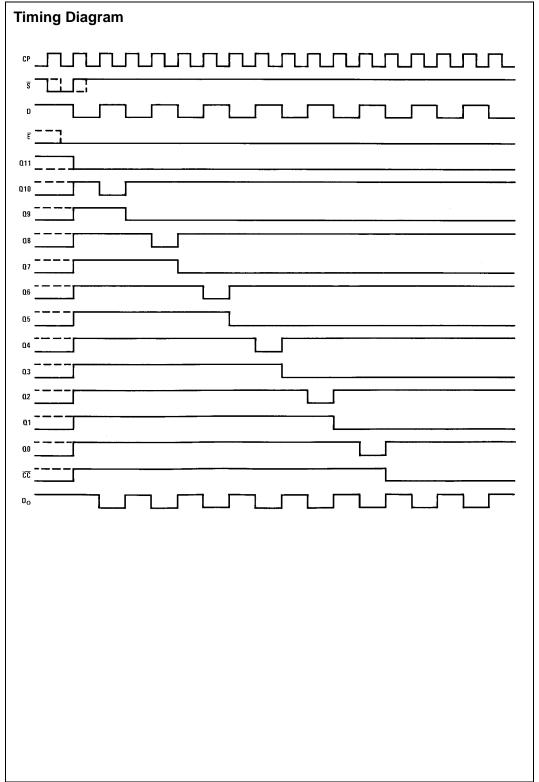

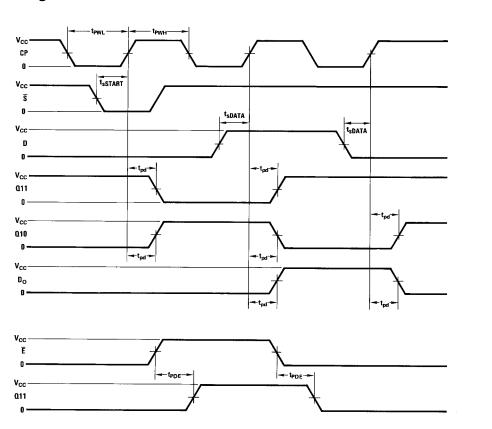

# **Switching Time Waveforms**

#### **USER NOTES FOR A/D CONVERSION**

The register can be used with either current switches that require a low voltage level to turn the switch ON or current switches that require a high voltage level to turn the switch ON. If current switches are used which turn ON with a low logic level, the resulting digit output from the register is active low. That is, a logic "1" is represented as a low voltage level. If current switches are used which turn ON with a high logic level, the resulting digit output is active high. A logic "1" is represented as a high voltage level.

For a maximum error of  $\pm 1\!\!/_2$  LSB, the comparator must be biased. If current switches that require a high voltage level to turn ON are used, the comparator should be biased  $\pm 1\!\!/_2$  LSB and if the current switches require a low logic level to turn ON, then the comparator must be biased  $\pm 1\!\!/_2$  LSB.

The register can be used to perform 2's complement conversion by offsetting the comparator one half full range  $\pm \frac{1}{2}$

LSB and using the complement of the MSB Q11 as the sign bit

If the register is truncated and operated in the continuous conversion mode, a lock-up condition may occur on power-ON. This situation can be overcome by making the START input the "OR" function of  $\overline{\text{CC}}$  and the appropriate register output.

The register, by suitable selection of register ladder network, can be used to perform either binary or BCD conversion

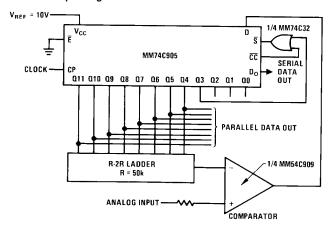

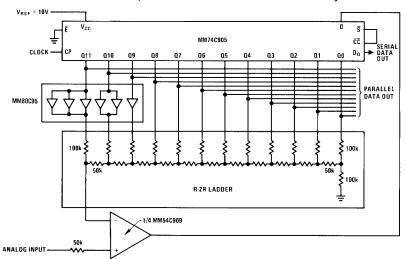

The register outputs can drive the 10 bits or less with 50k/ 100k R/2R ladder network directly for  $V_{CC}=10V$  or higher. In order to drive the 12-bit 50k/100k ladder network and have the  $\pm \frac{1}{2}$  LSB resolution, the MM74C902 or MM74C904 is used as buffers, three buffers for MSB (Q11), two buffers for Q10, and one buffer for Q9.

# **Typical Applications**

12-Bit Successive Approximation A-to-D Converter, Operating in Continuous 8-Bit Truncated Mode

12-Bit Successive Approximation A-to-D Converter, Operating in Continuous Mode, Drives the 50k/100k Ladder Network Directly

### **Definition of Terms**

CP: Register clock input.

**CC:** Conversion complete—this output remains at  $V_{OUT(1)}$  during a conversion and goes to  $V_{OUT(0)}$  when conversion is complete.

**D:** Serial *data* input—connected to comparator output in A-to-D applications.

$\overline{\bf E}$ : Register enable —this input is used to expand the length of the register. When  $\overline{\bf E}$  is at  $V_{IN(1)}$  Q11 is forced to  $V_{OUT(1)}$  and inhibits conversion. When not used for expansion  $\overline{\bf E}$  must be connected to  $V_{IN(0)}$  (GND).

Q11: True register MSB output.

Q11: Complement of register MSB output.

Qi (i = 0 to 11): Register outputs.

$\overline{\bf S}$ : Start input—holding start input at  $V_{IN(0)}$  for at least one clock period will initiate a conversion by setting MSB (Q11) at  $V_{OUT(0)}$  and all other output (Q10–Q0) at  $V_{OUT(1)}$ . If setup time requirements are met, a conversion may be initiated by holding start input at  $V_{IN(0)}$  for less than one clock period

**DO:** Serial data output—D input delayed by one clock period.

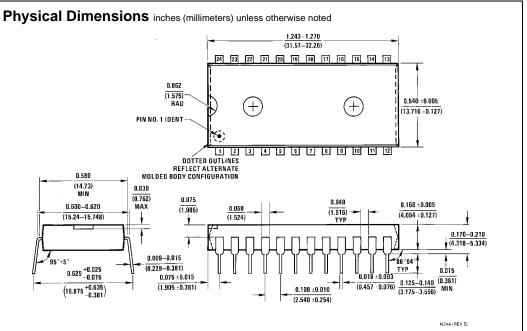

24-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-011, 0.600" Wide Package Number N24A

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com